ARM core Exception

예외처리란?

→ 실행 흐름상 오류가 발생했을 때 오류를 그대로 실행시키지 않고 오류에 대응하는 방법을 제시하는 개념이나 하드웨어 구조를 의미

RA6M3 제조사인 Renesas의 Reference Manual에는 예외처리 관련 메뉴얼이 없기 때문에

<ARM Cortex-M4 Technical Reference Manual> 혹은 <Armv7-M Architecture Reference Manual> 을 참고해야 함.

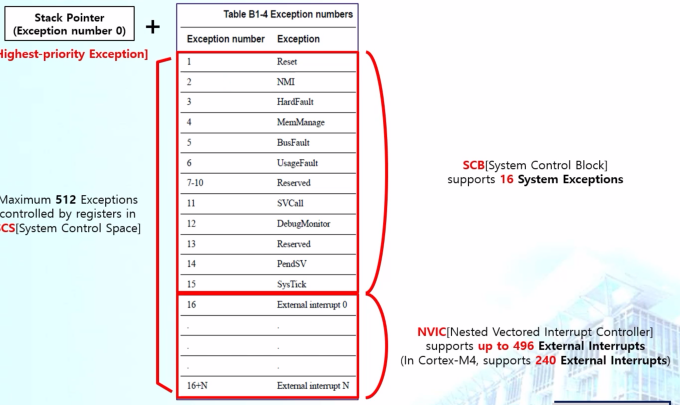

- 최상위단 0번 인덱스는 Stack Pointer 기능

- 총 512 exceptions 기능 구현 가능

- 이러한 기능들은 ARM프로세스의 특정 영역인 SCS(System Control Space)에서 관리

- 15번 SysTick은 내부 클럭

외부로치면 타이머를 통해 interrupt하는 기능과 유사 - 16번부턴 사용자 정의. 16 ~ 16+N 영역은 interrupt라고 할 수 있음

SCS(System Control Space)

- ARM프로세서의 모든 시스템적인 부분을 제어 및 관리하는 용도의 레지스터가 모두 여기에 포함.

- SCS영역은 최상위단에 위치

- SCB와 NVIC 모두 SCS안에 포함

NVIC(Nested Vectored Interrupt Controller)

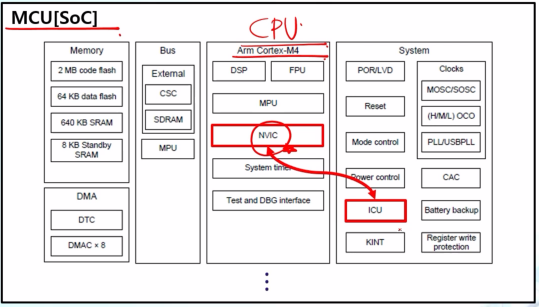

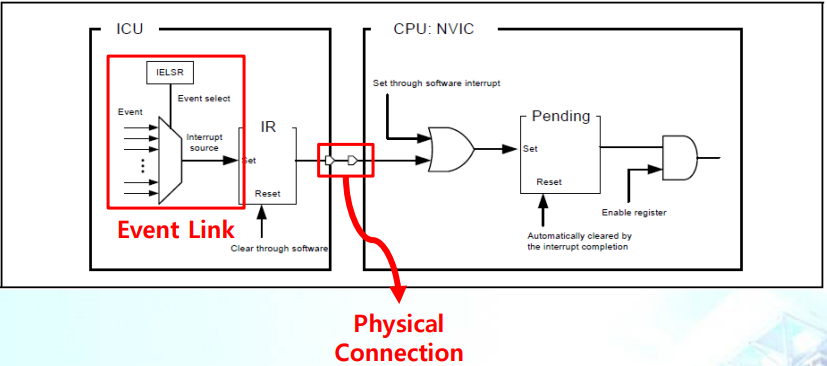

- 르네상스 MCU는 특이하게 NVIC만으로 Interrupt를 제어하지 않음

- NVIC는 ARM프로세서 내부에 존재하는 컨트롤러이고 외부에서도 Interrupt를 제어하는 ICU(Interrupt Controller Unit)가 있음 -> Renesas사에서 별도로 제공하는 것. ARM사의 표준 규약은 X

- NVIC와 ICU가 물리적으로 연결되어있어서 Interrupt를 외부에 있는 ICU먼저 거친 후 NVIC로 전달되는 구조

NVIC 개념

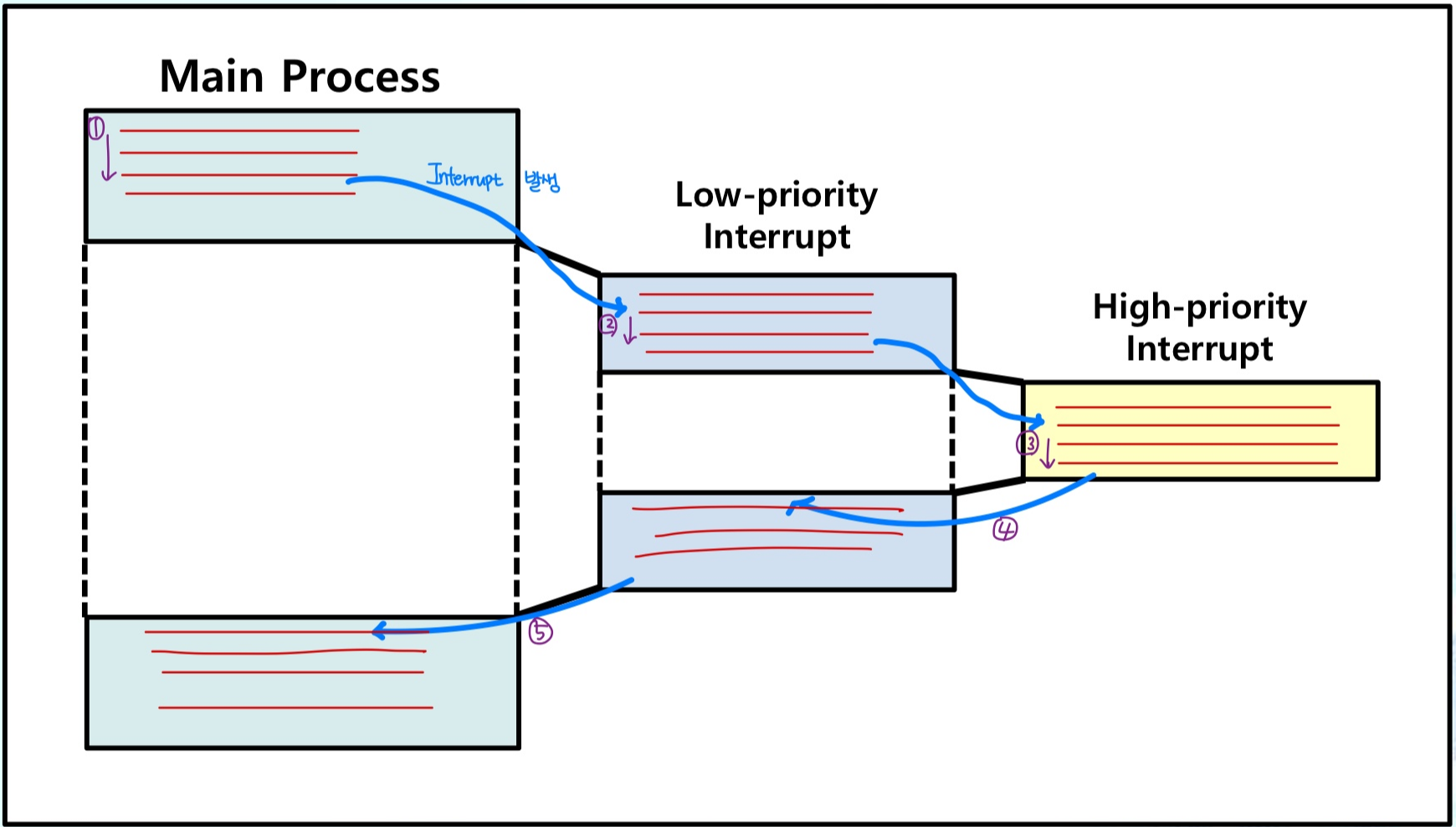

☞ NVIC make it possible that high-priority intrerrupt preempts low-priority interrupt.

thread가 여러 번 중첩되어 발생할 때 효과적으로 제어 가능하다하여 "Nested(중첩된)"라는 명칭이 붙음

장점

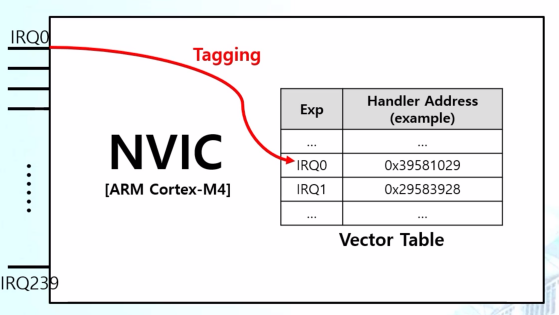

- 벡터 테이블로 저장되어있어 주소를 바로 찾을 수 있음

ex) IRQ0(Interrupt Request 0)이 발생했을 때, 해당되는 Interrupt handler를 통해 ISR로 접근하고 그 내용을 direct로 실행 가능

ICU(Interrupt Controller Unit)

ICU는 <ARM Reference Manual>에 존재하지 않고 <Renesas Reference Manual>에 존재

IELSR Register

특정 ICU 채널에서 어떤 event만을 받을 것인지 select 해주는 용도

여러 event가 multiplexer를 거쳐 특정 event를 select해서 넘겨주면 ICU에서 IR(정상적으로 Interrupt Request를 받았다는 status를 표시해주는 플래그)로 넘어오게 됨.

interrupt가 잘넘어오게 되면 자동으로 set이 되고 이 IR같은 경우는 수동으로 꼭 clear를 해줘야함(안한다면 다음 interrupt source를 받아들이지 못함).

이 후 pysical connection을 거쳐 최종적으로 CPU에서 처리가 되는 과정

ICU와 NVIC 연결 방법

ICU에서 보는 Event 정보와 NVIC에서 보는 IRQ정보는 완전히 일치하지 않음(매핑하기 나름)

ICU는 IELSR레지스터를 통해 event를 선택. 관문 역할

physical Connection 이후 부턴 내부적으로 매핑이 되어있기 때문에 건들 게 없고,

ICU의 특정 채널에서 어떤 event를 채택할 것인지만 따지면 됨

ex) channel 01 에서는 POIRT_IRQ0를 받겠다.

'Embedded' 카테고리의 다른 글

| [e2 studio] Expressions - 실시간으로 변수 값 확인하는 방법 (3) | 2024.03.14 |

|---|---|

| [HCS12] TIL (2) | 2024.03.12 |

| [RA6M3 ] TIL (03.11) (2) | 2024.03.11 |

>

>

![[RA6M3] TIL](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FG8sBQ%2FbtsFGUs1eBS%2FAAAAAAAAAAAAAAAAAAAAAKRLxVyJs1gfNFS5XlZ_jZ1q5n8XBHBPLF207y-dm7wG%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1772290799%26allow_ip%3D%26allow_referer%3D%26signature%3D3%252BS453chCl8aJD01hGBMNb5zw%252Bo%253D)